# **BAT32G137** Datasheet

Value-line Arm®-based 32-bit MCU with up to 128KB Flash,

Analog functions, Timers and Communication interfaces.

V2.50

Please be reminded about following SCT's policies on intellectual property

<sup>\*</sup> SINGAPORE CHANGI TECHNOLOGY PTE. LTD. (denoted as 'our company' for later use) has already applied for relative patents and entitled legal rights. Any patents related to SCT's MCU or other producrts is not authorized to use. Any individual, organization or company which infringes s our company's interlectual property rights will be forbidden and stopped by our company through any legal actions, and our company will claim the lost and required for compensation of any damage to the company.

<sup>\*</sup> The name of SINGAPORE CHANGI TECHNOLOGY PTE. LTD. and logo are both trademarks of our company.

<sup>\*</sup> Our company preserve the rights to further elaborate on the improvements about products' function, reliability and design in this manual. However, our company is not responsible for any usage about this munal. The applications and their purposes in this manual are just for clarification, our company does not guarantee that these applications are feasible without further improvements and changes, and our company does not recommend any usage of the products in areas where people's safety is endangered during accident. Our company's products are not authorzed to be used for life-saving or life support devices and systems.our company has the right to change or improve the product without any notification, for latest news, please visit our website: www.changitech.com.

#### **Features**

#### Ultra-low power consumption technology

- Operating Voltage:2.0V~5.5V

- ➤ Operating ambient temperature:-40°C~105°C

- > Low power modes:SLEEP, DEEPSLEEP

- Operating power consumption: RUN mode: 75uA/MHz@48MHz DEEPSLEEP mode:0.45uA DEEPSLEEP mode(+32.768K+RTC):0.7uA

#### Core

- > ARM®32-bitCortex®-M0+ CPU (MPU, MTB)

- Operating frequency:32KHz~48MHz

#### Memories

- ➤ 128KB Flash Memory: program/data flash

- > 1.5KB Special data flash memory

- > 12KB SRAM Memory(With Parity)

#### Reset and power management

- Power-on reset circuit.

- On-chip voltage detector (LVD) (Select interrupt and reset from 10 levels)

#### Clock

- High-speed on-chip oscillator, accuracy ±1%. Select from 1MHz to 64MHz (CPU:1MHz to 48MHz)

- ➤ Low-speed on-chip oscillator: 15KHz

- ➤ Main clock oscillator: 1MHz to 20MHz

- ➤ Sub clock oscillator: 32.768KHz

#### Multiplier/divider

- Single-cycle integer multiplier

- ➤ 4-cycle or 8-cycle integer divider

#### DMA

- Interupt trigger start.

- Transfer modes: Normal mode, Repeat mode, Block mode and Chain transfers mode

- > Transfer space: 4 GB area from 0000 0000h to FFFF FFFFh except reserved areas

#### EVENTC

- Event Link Controller

- Event signals(22 types) can be used as activation sources for operating any one of 10 types of peripheral functions

#### GPIO

- > I/O port:29 to 59

- Can be set to N-ch open drain, TTL input buffer, and on-chip pull-up resistor

- On-chip key interrupt function

- On-chip clock output/buzzer output controller

#### Serial wire debug (SWD)

#### Timers

- > 16-bit timer: 9 channels

- > 15-bit interval timer: 1 channel

- > Real-time clock(RTC): 1 channel

- Watchdog timer(WWDT): 1 channel (operable with the dedicated low-speed on-chip oscillator)

- SysTick timer

#### Serial interfaces

- > SPI:1 channel; Sample SPI:3 to 6 channels

- UART:3 channels (LIN-bus)

- > I2C:1 channel; Sample I2C:3 to 6 channels

- > IrDA:1 channel

- > CAN:1 channel

#### Safety

- ➤ IEC/UL 60730

- Illegal memory access

- > SRAM Parity Error Check

- Cyclic Redundancy Check (CRC) Calculator

- > SFR protection

- > 128-bit unique ID

- Flash secondary protection in debug mode ( level1: only erase the entire area of flash; level2 the emulator connection is invalid)

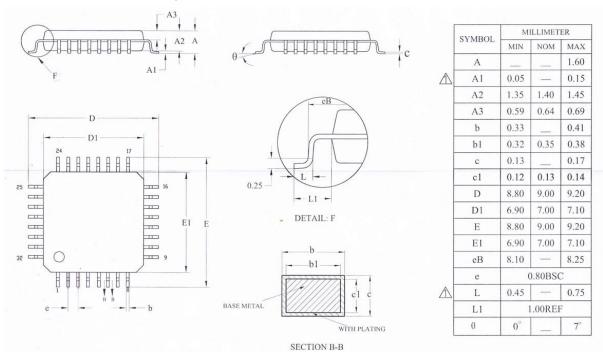

#### Packages

> 32/48/64LQFP,40QFN

#### Analog

> 12-Bit A/D Converter

Conversion range: 0 to Vrefp or VDD Analog input: Up to 16 channels, Internal reference voltage (1.45 V) and temperature sensor

Conversionrate: 1.06Msps

> 8-Bit D/A Converter (DAC8) × 2

- Comparator(CMP) x 2:The external reference voltage or internal reference voltage can be selected as the reference voltage

- Programmable gain amplifier(PGA)×2: GAIN X4/8/10/12/14/16/32Can be selected

# 1 Overview

### 1.1 Introduction

The ultra-low-power BAT32G137 incorporates a high-performance ARM®Cortex®-M0+ 32-bit RISC core running up to 48 MHz and high-speed embedded flash memory (SRAM maximum 12KB, program/data flash 128KB). This product integrates I2C, SPI, UART, LIN multiple standard interfaces. Integrated 12bitA/D converter, temperature sensor, 8bitD/A converter, comparator, programmable gain amplifier. Among them, the 12bitA/D converter can collect external sensor signals to reduce the system design cost. The 8-bit D/A converter can be used for audio playback or power control. The temperature integrated sensor can realize real-time monitoring of the external ambient temperature. The integrated comparator can support both high-speed and low-speed operating modes. In high-speed mode, it can support feedback control of high-speed motor operation. And in low-speed mode, it can be used for battery monitoring. Integrated multiple advanced timer modules.

BAT32G137 has particularly excellent low-power performance, with two low-power modes of sleep and deep sleep, to flexible design for users. Its operating power consumption is 75uA/MHz@48MHz, and the power consumption in deep sleep mode is only 0.45uA, which is suitable for battery-powered low-power devices. At the same time, due to the integrated event link controller, direct connection between hardware modules can be achieved without CPU intervention, which is faster than the use of interrupt response, while reducing the CPU's activity frequency and extending battery life.

These characteristics make the BAT32G137 microcontroller series widely applicable to consumer civilian products, such as motor drive control, home appliances and mobile devices.

www.changitech.com 4 / 75 Rev.2.50

# 1.2 Ordering Information

B A T 32 G 1 37 G H 64 FB

Package type (NA/NB:QFN, FA/FB/FP:LQFP)

Pin count (64pin, 48pin, 40pin, 32pin)

flash memory size (H:128KB, E:64KB, C:32KB)

Operating temperature: -40~105°C

product code: 37

CPU: Cortex-M0+

application (G: General series)

Bus: 32bit

Family name: BAT

Figure 1 - 1 Part Number, Memory Size, and Package of BAT/G137

#### **Product list:**

| Pin count | Package                        | Application                                    | Ordering Part Number |

|-----------|--------------------------------|------------------------------------------------|----------------------|

| 32 pins   | 32LQFP (7x7mm, 0.8mm pitch)    | Consumption Home appliances Industrial control | BAT32G137GH32FP      |

| 40 pins   | 40QFN<br>(5x5mm, 0.4mm pitch)  | Consumption Home appliances Industrial control | BAT32G137GH40NB      |

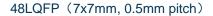

| 48 pins   | 48LQFP<br>(7x7mm, 0.5mm pitch) | Consumption Home appliances Industrial control | BAT32G137GH48FA      |

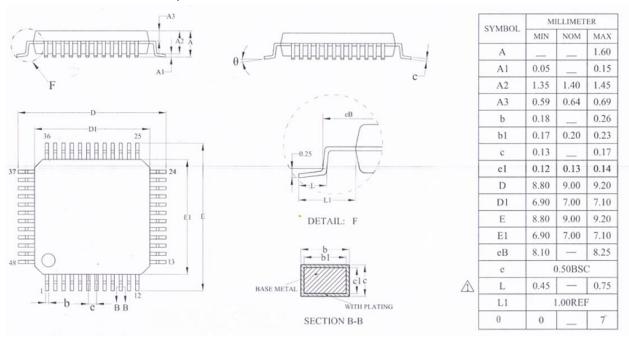

| 64 pins   | 64LQFP<br>(7x7mm, 0.4mm pitch) | Consumption Home appliances Industrial control | BAT32G137GH64FB      |

#### FLASH, SRAM:

| Flash  | Special data | SRAM | BAT32G137       |               |  |  |

|--------|--------------|------|-----------------|---------------|--|--|

| memory | flash memory |      | 32 Pins 40 Pins |               |  |  |

| 128KB  | 1.5KB        | 12KB | BAT32G137GH32   | BAT32G137GH40 |  |  |

| Flash  | Special data | SRAM | BAT32G137                   |  |  |  |

|--------|--------------|------|-----------------------------|--|--|--|

| memory | flash memory |      | 48 Pins 64 Pins             |  |  |  |

| 128KB  | 1.5KB        | 12KB | BAT32G137GH48 BAT32G137GH64 |  |  |  |

# 1.3 Pin Configuration (Top View)

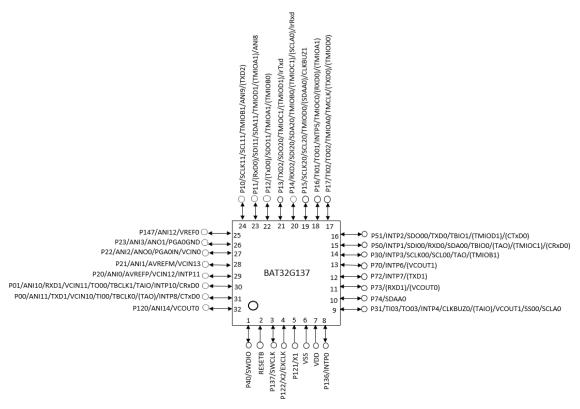

# 1.3.1 32-pin products

32LQFP (7x7mm, 0.8mm pitch)

Remark: Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.changitech.com 6 / 75 Rev.2.50

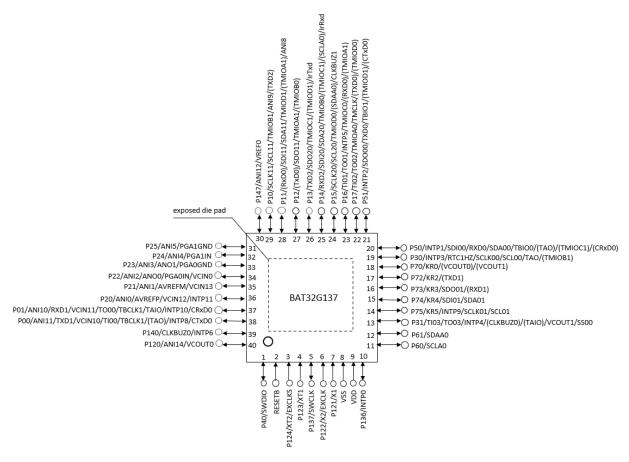

# 1.3.2 40-pin products

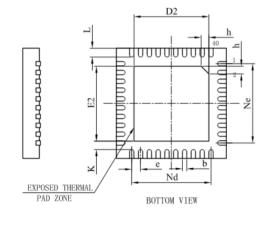

40QFN (5x5mm, 0.4mm pitch)

Remark: Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

www.changitech.com 7 / 75 Rev.2.50

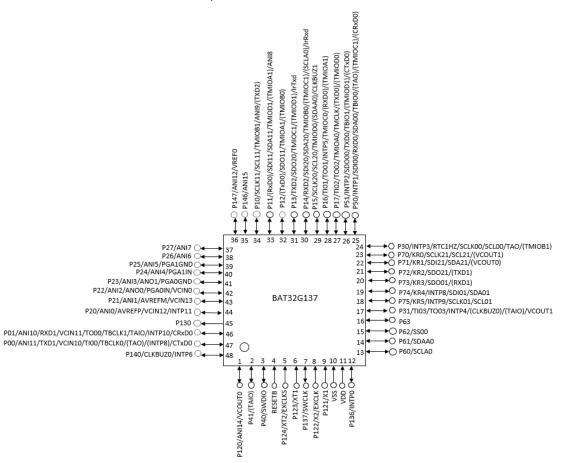

# 1.3.3 48-pin products

48LQFP (7x7mm, 0.5mm pitch)

Remark: Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

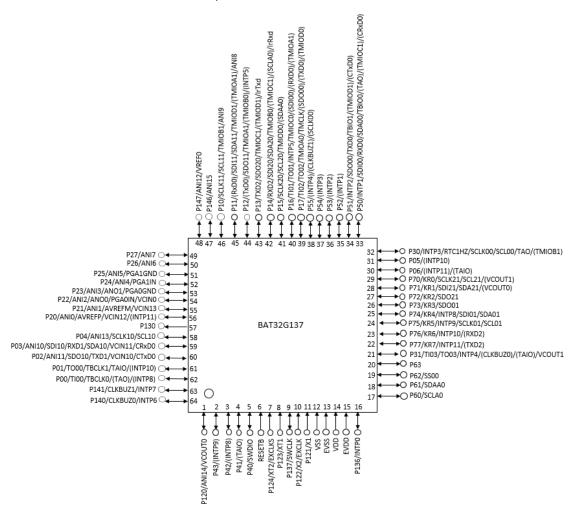

## 1.3.4 64-pin products

64LQFP (7x7mm, 0.4mm pitch)

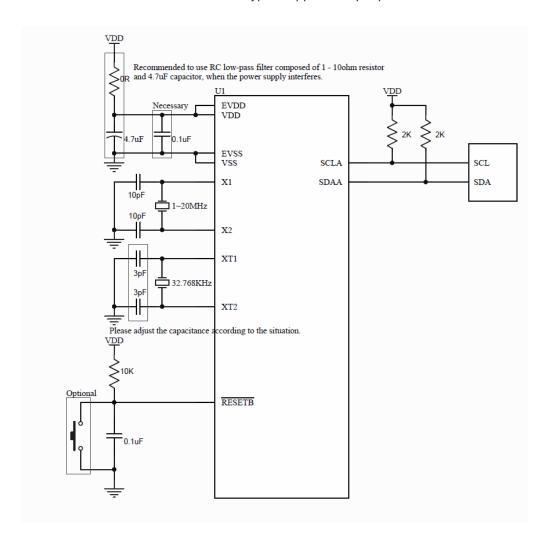

- Caution 1. Make EVSS pin the same potential as VSS pin.

- Caution 2. Make EVDD pin the same potential as VDD pin.

- Remark 1. When using the microcontroller for an application where the noise generated inside the microcontroller must be reduced,

it is recommended to supply separate powers to the VDD and EVDD pins and connect the Vss and EVss pins to separate ground lines.

Remark 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

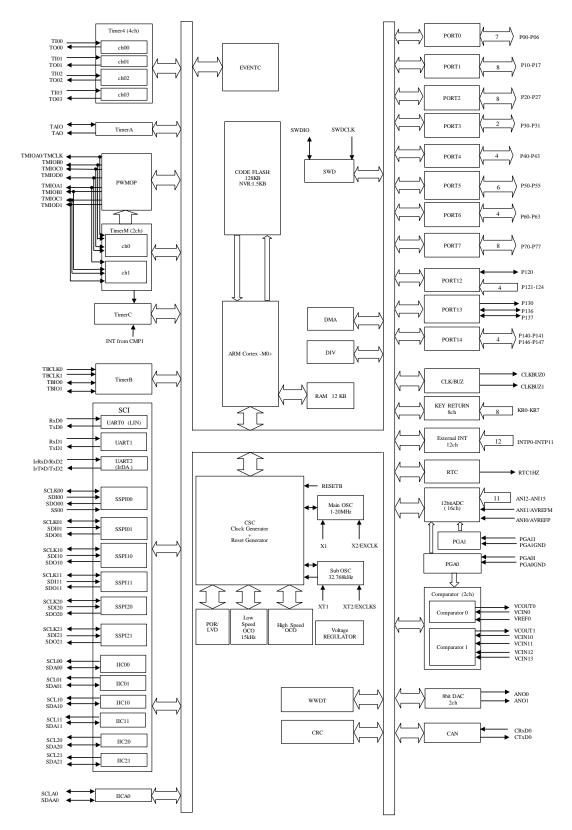

# 2 Block Diagram

Note: this is a block diagram of 64-pin products, some functions of products below 64 pins are not supported

# 3 Memory Space

| FFFF_FFFFH               | Reserved                        |  |  |

|--------------------------|---------------------------------|--|--|

| E00F_FFFFH E000_0000H    | Cortex-M0+ internal peripherals |  |  |

|                          | Reserved                        |  |  |

| 4005_FFFFH               | Peripherals                     |  |  |

| 4000_0000H               | Reserved                        |  |  |

| 2000_2FFFH<br>2000_0000H | SRAM (12KB)                     |  |  |

|                          | Reserved                        |  |  |

| 0050_05FFH<br>0050_0000H | data flash(1.5KB)               |  |  |

|                          | Reserved                        |  |  |

| 0001_FFFFH               | code flash(128KB)               |  |  |

| 0000_0000H               |                                 |  |  |

www.changitech.com 11 / 75 Rev.2.50

# **4 PIN Funtions**

# 4.1 Port Functions

Pin I/O buffer power supplies depend on the product. The relationship between these power supplies and the pins are shown below.

#### 64-pin product:

| Power Supply | Corresponding Pins                                       |

|--------------|----------------------------------------------------------|

| EVDD/EVSS    | Port pins other than P20~P27, P121~P124, P137 and RESETB |

| VDD/VSS      | P20~P27, P121~P124, P137 and RESETB                      |

Products other than 64 pins use a single power supply, all pins are powered by VDD.

www.changitech.com 12 / 75 Rev.2.50

# 4.1.1 32-pin products

(1/2)

| Function |     | After Reset     |                                         |                                               |

|----------|-----|-----------------|-----------------------------------------|-----------------------------------------------|

| Name     | I/O | Release         | Alternate Function                      | Function                                      |

|          |     |                 | ANI11/TXD1/VCIN10/TI00/TBCLK0/(TAO)     | Port 0.                                       |

| P00      |     |                 | /INTP8/CTxD0                            | 2-bit I/O port.                               |

|          |     |                 |                                         | Input/output can be specified in 1-bit units. |

|          |     |                 |                                         | Use of an on-chip pull-up resistor can be     |

|          |     |                 |                                         | specified                                     |

|          | I/O | Analog          |                                         | by a software setting at input port.          |

| P01      |     | function        | ANI10/RXD1/VCIN11/TO00/TBCLK1           | Input of P01 can be set to TTL input buffer.  |

|          |     |                 | /TAIO/INTP10/CRxD0                      | Output of P00 can be set to N-ch open-        |

|          |     |                 |                                         | drain                                         |

|          |     |                 |                                         | output (VDD tolerance).                       |

|          |     |                 |                                         | P00 and P01 can be set to analog input        |

| P10      |     | Analog          | SCLK11/SCL11/TMIOB1/ANI9/(TXD2)         | Port 1.                                       |

| P11      |     | function        | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8 | 8-bit I/O port.                               |

| P12      |     |                 | (TxD0)/SDO11/TMIOA1/(TMIOB0)            | Input/output can be specified in 1-bit units. |

| P13      |     | O<br>Input port | TxD2/SDO20/TMIOC1/(TMIOD1)/IrTxd        | Use of an on-chip pull-up resistor can be     |

|          |     |                 | RxD2/SDI20/SDA20/ TMIOB0/(TMIOC1)/      | specified                                     |

| P14      |     |                 | (SCLA0)/IrRxd                           | by a software setting at input port.          |

| P15      | I/O |                 | SCLK20/SCL20/TMIOD0/(SDAA0)/CLKBUZ1     | Input of P10 and P14 to P17 can be set to     |

| P16      | 1/0 |                 | TI01/TO01/INTP5/TMIOC0/(RXD0)/(TMIOA1)  | TTL                                           |

|          |     |                 | TI02/TO02/TMIOA0/TMCLK/(TXD0)/(TMIOD0)  | input buffer.                                 |

|          |     |                 |                                         | Output of P10, P11, P13 to P15, and P17       |

| D47      |     |                 |                                         | can be                                        |

| P17      |     |                 |                                         | set to N-ch open-drain output (VDD            |

|          |     |                 |                                         | tolerance).                                   |

|          |     |                 |                                         | P10 to P11 can be set to analog input.        |

| P20      |     |                 | ANI0/AVREFP/VCIN12/(INTP11)             | Port 2.                                       |

| P21      | I/O | Analog          | ANI1/AVREFM/VCIN13                      | 4-bit I/O port.                               |

| P22      | 1/0 | function        | ANI2/ANO0/PGA0IN/VCIN0                  | Input/output can be specified in 1-bit units. |

| P23      |     |                 | ANI3/ANO1/PGA0GND                       | Can be set to analog input.                   |

| P30      |     |                 | INTP3/SCLK00/SCL00/TAO/(TMIOB1)         | Port 3.                                       |

|          |     |                 |                                         | 2-bit I/O port.                               |

|          |     |                 |                                         | Input/output can be specified in 1-bit units. |

|          |     |                 |                                         | Use of an on-chip pull-up resistor can be     |

| P31      | I/O | Input port      | TI03/TO03/INTP4/CLKBUZ0/(TAIO)/VCOUT1   | specified                                     |

| 1-31     |     |                 | /SS00/SCLA0                             | by a software setting at input port.          |

|          |     |                 |                                         | Input of P30 and P31 can be set to TTL        |

|          |     |                 |                                         | input                                         |

|          |     |                 |                                         | buffer.                                       |

|         |            |                 |                                           | Output of P30 and P31 can be set to N-ch Open-drain output (VDD tolerance). |

|---------|------------|-----------------|-------------------------------------------|-----------------------------------------------------------------------------|

|         |            |                 |                                           | Port 4.                                                                     |

|         |            |                 |                                           | 1-bit I/O port.                                                             |

| P40 I/O | 1/0        | la a cot a a at | OMBIO                                     | Input/output can be specified.                                              |

|         | Input port | ut port SWDIO   | Use of an on-chip pull-up resistor can be |                                                                             |

|         |            |                 |                                           | specified                                                                   |

|         |            |                 |                                           | by a software setting at input port.                                        |

(2/2)

| Function | I/O  | After Reset        | Alternate Function                                    | Function                                                                                                                                                                                                         |

|----------|------|--------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | 1/0  | Release            | Alternate Function                                    | Function                                                                                                                                                                                                         |

| P50      |      | Input port         | INTP1/SDI00/RXD0/SDA00/TBIO0/(TAO) /(TMIOC1) /(CRxD0) | Port 5.  2-bit I/O port. Input/output can be specified in 1-bit units.                                                                                                                                           |

| P51      | I/O  |                    | INTP2/SDO00/TXD0/TBIO1/(TMIOD1)/(CTxD 0)              | Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P50 can be set to TTL input buffer. Output of P50 and P51 can be set to N-ch opendrain output (VDD tolerance). |

| P70      |      |                    | INTP6/(VCOUT1)                                        | Port 7.                                                                                                                                                                                                          |

| P72      |      |                    | INTP7/(TXD1)                                          | 4-bit I/O port. Input/output can be specified.                                                                                                                                                                   |

| P73      | I/O  | Input port         | (RXD1)/(VCOUT0)                                       | Use of an on-chip pull-up resistor can be                                                                                                                                                                        |

| P74      | ,,,, |                    | SDAA0                                                 | specified by a software setting at input port.  Input of P74 can be set to TTL input buffer.  Output of P74 can be set to N-ch open-drain output (VDD tolerance).                                                |

| P120     | I/O  | Analog function    | ANI14/VCOUT0                                          | Port 12. 1-bit I/O port and 2-bit input-only port.                                                                                                                                                               |

| P121     |      |                    | X1                                                    | For only P120, input/output can be specified.                                                                                                                                                                    |

| P122     | I    | Input port         | X2/EXCLK                                              | For only P120, use of an on-chip pull-up resistor can be specified by a software setting at input port. P120 can be set to analog input.                                                                         |

| P136     | 1/0  | lancet a set       | INTP0                                                 | Port 13.                                                                                                                                                                                                         |

| P137     | I/O  | Input port         | SWCLK                                                 | 2-bit I/O port.                                                                                                                                                                                                  |

| P147     | I/O  | Analog<br>function | ANI12/VREF0                                           | Port 14.  1-bit I/O port. Input/output can be specified. Use of an on-chip pull-up resistor can be specified by a software setting at input port. P147 can be set to analog input.                               |

| RESETB   | 1    | _                  | _                                                     | Input-only pin for external reset.  Connect to VDD directly or via a resistor when external reset is not used.                                                                                                   |

**Note** Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units). Description of Alternate function, please refer to "4.2 pins other than port pins".

Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

# 4.1.2 40-pin products

(1/2)

| Function |     | After Reset        | Altamata Function                                | Function                                                                                                                                                                                                                                                   |

|----------|-----|--------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     | 1/0 | Release            | Alternate Function                               | Function                                                                                                                                                                                                                                                   |

| Doo      |     | Analog<br>function | ANI11/TXD1/VCIN10/TI00/TBCLK0/(TAO)              | Port 0.                                                                                                                                                                                                                                                    |

| P00      | I/O |                    | /INTP8/CTxD0                                     | 2-bit I/O port.  Input/output can be specified in 1-bit units.                                                                                                                                                                                             |

| P01      |     |                    | ANI10/RXD1/VCIN11/TO00/TBCLK1 /TAIO/INTP10/CRxD0 | Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P01 can be set to TTL input buffer. Output of P00 can be set to N-ch open-drain output(VDD tolerance).  P00 and P01 can be set to analog input           |

| P10      |     | Analog             | SCLK11/SCL11/TMIOB1/ANI9/(TXD2)                  | Port 1.                                                                                                                                                                                                                                                    |

| P11      |     | function           | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8          | 8-bit I/O port.                                                                                                                                                                                                                                            |

| P12      |     |                    | (TxD0)/SDO11/TMIOA1/(TMIOB0)                     | Input/output can be specified in 1-bit units.                                                                                                                                                                                                              |

| P13      |     |                    | TxD2/SDO20/TMIOC1/(TMIOD1)/IrTxd                 | Use of an on-chip pull-up resistor can be specified by a software setting at input port.                                                                                                                                                                   |

| P14      | I/O |                    | RxD2/SDI20/SDA20/ TMIOB0/(TMIOC1)/               | Input of P10 and P14 to P17 can be set to TTL                                                                                                                                                                                                              |

| P14      |     | Input port         | (SCLA0)/IrRxd                                    | input buffer.  Output of P10, P11, P13 to P15, and P17 can                                                                                                                                                                                                 |

| P15      |     |                    | SCLK20/SCL20/TMIOD0/(SDAA0)/CLKBUZ1              | be set to N-ch open-drain output (VDD                                                                                                                                                                                                                      |

| P16      |     |                    | TI01/TO01/INTP5/TMIOC0/(RXD0)/(TMIOA1)           | tolerance).                                                                                                                                                                                                                                                |

| P17      |     |                    | TI02/TO02/TMIOA0/TMCLK/(TXD0)/(TMIOD0)           | P10 to P11 can be set to analog input.                                                                                                                                                                                                                     |

| P20      |     |                    | ANI0/AVREFP/VCIN12/(INTP11)                      |                                                                                                                                                                                                                                                            |

| P21      |     |                    | ANI1/AVREFM/VCIN13                               | Port 2.                                                                                                                                                                                                                                                    |

| P22      | I/O | Analog             | ANI2/ANO0/PGA0IN/VCIN0                           | 6-bit I/O port.                                                                                                                                                                                                                                            |

| P23      | 1/0 | function           | ANI3/ANO1/PGA0GND                                | Input/output can be specified in 1-bit units.                                                                                                                                                                                                              |

| P24      |     |                    | ANI4/PGA1IN                                      | Can be set to analog input.                                                                                                                                                                                                                                |

| P25      |     |                    | ANI5/PGA1GND                                     |                                                                                                                                                                                                                                                            |

| P30      |     |                    | INTP3/RTC1HZ/SCLK00/SCL00/TAO                    | Port 3. 2-bit I/O port.                                                                                                                                                                                                                                    |

| P31      | I/O | Input port         | TI03/TO03/INTP4/CLKBUZ0/(TAIO)/SS00              | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specified by a software setting at input port.  Input of P30 can be set to TTL input buffer.  Output of P30 can be set to N-ch open-drain output (VDD tolerance). |

| P40      | I/O | Input port         | SWDIO                                            | Port 4.  1-bit I/O port. Input/output can be specified. Use of an on-chip pull-up resistor can be specified by a software setting at input port.                                                                                                           |

(2/2)

| Function | I/O | After Reset        | Alternate Function                      | Function                                                                                                                                                                                                          |

|----------|-----|--------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name     |     | Release            |                                         | Dort 5                                                                                                                                                                                                            |

| P50      |     |                    | INTP1/SDI00/RXD0/SDA00/TBIO0/(TAO)      | Port 5. 2-bit I/O port.                                                                                                                                                                                           |

| 1 30     |     |                    | /(TMIOC1)/(CRxD0)                       | Input/output can be specified in 1-bit units.                                                                                                                                                                     |

| P51      | I/O | Input port         | INTP2/SDO00/TXD0/TBIO1/(TMIOD1)/(CTxD0) | Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P50 can be set to TTL input buffer. Output of P50 and P51 can be set to N-ch open-drain output (VDD tolerance). |

| P60      |     |                    | SCLA0                                   | Port 6.                                                                                                                                                                                                           |

| P61      | I/O | I/O Input port     | SDAA0                                   | 2-bit I/O port. Input/output can be specified in 1-bit units. Output of P60 and P61 is N-ch open-drain output (6 V tolerance).                                                                                    |

| P70      |     |                    | KR0/(VCOUT0)/(VCOUT1)                   | Port 7.                                                                                                                                                                                                           |

| P72      |     |                    | KR2/(TXD1)                              | 5-bit I/O port. Input/output can be specified.                                                                                                                                                                    |

| P73      | I/O | Input port         | KR3/SDO01/(RXD1)                        | Use of an on-chip pull-up resistor can be                                                                                                                                                                         |

| P74      |     |                    | KR4/SDI01/SDA01                         | specified by a software setting at input port.  Output of P74 can be set to N-ch open                                                                                                                             |

| P75      |     |                    | KR5/INTP9/SCLK01/SCL01                  | -drain output (VDD tolerance).                                                                                                                                                                                    |

| P120     | I/O | Analog function    | ANI14/VCOUT0                            | Port 12.                                                                                                                                                                                                          |

| P121     |     |                    | X1                                      | 1-bit I/O port and 2-bit input-only port.  For only P120, input/output can be specified.                                                                                                                          |

| P122     |     | Input port         | X2/EXCLK                                | For only P120, inpuroutput can be specified.  For only P120, use of an on-chip pull-up                                                                                                                            |

| P123     |     | Input port         | XT1                                     | resistor can be specified by a software setting                                                                                                                                                                   |

| P124     |     |                    | XT2/EXCLKS                              | at input port. P120 can be set to analog input.                                                                                                                                                                   |

| P136     |     |                    | INTP0                                   | Port 13.                                                                                                                                                                                                          |

| P137     | I/O | Input port         | SWCLK                                   | 2-bit I/O port.                                                                                                                                                                                                   |

| P140     |     | Input port         | CLKBUZ0/INTP6                           | Port 14.                                                                                                                                                                                                          |

| P147     | I/O | Analog<br>function | ANI12/VREF0                             | 2-bit I/O port. Input/output can be specified. Use of an on-chip pull-up resistor can be specified by a software setting at input port. P147 can be set to analog input.                                          |

| RESETB   | 1   | _                  | _                                       | Input-only pin for external reset.  Connect to VDD directly or via a resistor  When external reset is not used.                                                                                                   |

**Note** Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units). Description of Alternate function, please refer to "4.2 pins other than port pins".

Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

# 4.1.3 48-pin products

(1/2)

| Function<br>Name | I/O   | After Reset<br>Release | Alternate Function                                                  | Function                                                                                                                                                                                                                                         |

|------------------|-------|------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00              |       | Analog<br>function     | ANI11/TXD1/VCIN10/TI00/TBCLK0/(TAO) /(INTP8)/CTxD0                  | Port 0. 2-bit I/O port. Input/output can be specified in 1-bit units.                                                                                                                                                                            |

| P01              | 1// 1 |                        | ANI10/RXD1/VCIN11/TO00/TBCLK1 /TAIO/INTP10/CRxD0                    | Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P01 can be set to TTL input buffer. Output of P00 can be set to N-ch open-drain output(VDD tolerance).  P00 and P01 can be set to analog input |

| P10              |       | Analog                 | SCLK11/SCL11/TMIOB1/ANI9/(TXD2)                                     |                                                                                                                                                                                                                                                  |

| P11              |       | function               | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8                             | Port 1.                                                                                                                                                                                                                                          |

| P12              |       |                        | (TxD0)/SDO11/TMIOA1/(TMIOB0)                                        | 8-bit I/O port. Input/output can be specified in 1-bit units.                                                                                                                                                                                    |

| P13              |       |                        | TxD2/SDO20/TMIOC1/(TMIOD1)/IrTxd                                    | Use of an on-chip pull-up resistor can be                                                                                                                                                                                                        |

| P14              | I/O   |                        | RxD2/SDI20/SDA20/ TMIOB0/(TMIOC1)/<br>(SCLA0)/IrRxd                 | specified by a software setting at input port.  Input of P10 and P14 to P17 can be set to TTL input buffer.                                                                                                                                      |

| P15              |       | Input port             | SCLK20/SCL20/TMIOD0/(SDAA0)/CLKBUZ1                                 | Output of P10, P11, P13 to P15, and P17 can                                                                                                                                                                                                      |

| P16              |       |                        | TI01/TO01/INTP5/TMIOC0/(RXD0)/(TMIOA1)                              | be set to N-ch open-drain output (VDD tolerance).                                                                                                                                                                                                |

| P17              |       |                        | TI02/TO02/TMIOA0/TMCLK0/(TXD0) /(TMIOD0)                            | P10 to P11 can be set to analog input.                                                                                                                                                                                                           |

| P20              |       |                        | ANIO/AVREFP/VCIN12/(INTP11)                                         |                                                                                                                                                                                                                                                  |

| P21              |       |                        | ANI1/AVREFM/VCIN13                                                  |                                                                                                                                                                                                                                                  |

| P22              |       | ANI2/ANO0/PGA0IN       | ANI2/ANO0/PGA0IN/VCIN0                                              |                                                                                                                                                                                                                                                  |

| P23              |       | Analog                 | ANI3/ANO1/PGA0GND                                                   | Port 2.<br>8-bit I/O port.                                                                                                                                                                                                                       |

| P24              | I/O   | function               | ANI4/PGA1IN                                                         | Input/output can be specified in 1-bit units.                                                                                                                                                                                                    |

| P25              |       |                        | ANI5/PGA1GND                                                        | Can be set to analog input.                                                                                                                                                                                                                      |

| P26              |       |                        | ANI6                                                                |                                                                                                                                                                                                                                                  |

| P27              | _     |                        | ANI7                                                                |                                                                                                                                                                                                                                                  |

| P30              |       |                        | INTP3/RTC1HZ/SCLK00/SCL00/TAO                                       | Port 3. 2-bit I/O port.                                                                                                                                                                                                                          |

| P30              |       |                        | /(TMIOB1)                                                           | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be                                                                                                                                                         |

| P31              | I/O   | Input port             | TI03/TO03/INTP4/(CLKBUZ0)/(TAIO)                                    | specified by a software setting at input port. Input of P30 can be set to TTL input buffer.                                                                                                                                                      |

|                  |       | /VCOUT1                | Output of P30 can be set to N-ch open-drain output (VDD tolerance). |                                                                                                                                                                                                                                                  |

| P40              |       |                        | SWDIO                                                               | Port 4.                                                                                                                                                                                                                                          |

| P41              | I/O   | Input port             | (TAIO)                                                              | 2-bit I/O port. Input/output can be specified. Use of an on-chip pull-up resistor can be specified by a software setting at input port.                                                                                                          |

(2/2)

| Function<br>Name | I/O | After Reset<br>Release | Alternate Function                                   | Function                                                                                                                                                                                                          |

|------------------|-----|------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P50              | I/O |                        | INTP1/SDI00/RXD0/SDA00/TBIO0/(TAO) /(TMIOC1)/(CRxD0) | Port 5. 2-bit I/O port. Input/output can be specified in 1-bit units.                                                                                                                                             |

| P51              |     | Input port             | INTP2/SDO00/TXD0/TBIO1/(TMIOD1)/(CTxD0)              | Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P50 can be set to TTL input buffer. Output of P50 and P51 can be set to N-ch open-drain output (VDD tolerance). |

| P60              |     |                        | SCLA0                                                | Port 6.                                                                                                                                                                                                           |

| P61              |     |                        | SDAA0                                                | 4-bit I/O port.                                                                                                                                                                                                   |

| P62              | I/O | Input port             | SS00                                                 | Input/output can be specified in 1-bit units.  Output of P60 and P63 is N-ch open-drain output                                                                                                                    |

| P63              |     |                        | _                                                    | (6 V tolerance).                                                                                                                                                                                                  |

| P70              |     |                        | KR0/SCLK21/SCL21/(VCOUT1)                            | Post 7                                                                                                                                                                                                            |

| P71              |     |                        | KR1/SDI21/SDA21/(VCOUT0)                             | Port 7. 6-bit I/O port.                                                                                                                                                                                           |

| P72              |     | Input port             | KR2/SDO21/(TXD1)                                     | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specific by a software setting at input port.                                                                            |

| P73              | I/O |                        | KR3/SDO01/(RXD1)                                     |                                                                                                                                                                                                                   |

| P74              |     |                        | KR4/INTP8/SDI01/SDA01                                | Output of P71 and P74 can be set to N-ch                                                                                                                                                                          |

| P75              |     |                        | KR5/INTP9/SCLK01/SCL01                               | open-drain output (VDD tolerance).                                                                                                                                                                                |

| P120             | I/O | Analog function        | ANI14/VCOUT0                                         | Port 12.  1-bit I/O port and 2-bit input-only port.                                                                                                                                                               |

| P121             |     |                        | X1                                                   | For only P120, input/output can be specified.                                                                                                                                                                     |

| P122             |     | Input port             | X2/EXCLK                                             | For only P120, use of an on-chip pull-up                                                                                                                                                                          |

| P123             |     | Input port             | XT1                                                  | resistor can be specified by a software setting at input port. P120 can be set to                                                                                                                                 |

| P124             |     |                        | XT2/EXCLKS                                           | analog input.                                                                                                                                                                                                     |

| P130             | 0   | Output port            | _                                                    |                                                                                                                                                                                                                   |

| P136             | 1/0 | Input port             | INTP0                                                | Port 13.  1-bit output-only port and 2-bit I/O port.                                                                                                                                                              |

| P137             | 1/0 | I/O Input port         | SWCLK                                                | 1-bit output-only port and 2-bit #0 port.                                                                                                                                                                         |

| P140             |     | Input port             | CLKBUZ0/INTP6                                        | Port 14.                                                                                                                                                                                                          |

| P146             |     |                        | ANI15                                                | 3-bit I/O port. Input/output can be specified.                                                                                                                                                                    |

| P147             | I/O | O Analog function      | ANI12/VREF0                                          | Use of an on-chip pull-up resistor can be specified by a software setting at input port. P146 and P147 can be set to analog input.                                                                                |

| RESETB           | I   | _                      | _                                                    | Input-only pin for external reset.  Connect to VDD directly or via a resistor when external reset is not used.                                                                                                    |

**Note** Each pin can be specified as either digital or analog by setting port mode control register x (PMCx) (Can be specified in 1-bit units). Description of Alternate function, please refer to "4.2 pins other than port pins".

Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register.

# 4.1.4 64-pin products

(1/2)

|                  |     |                        |                                                     | · · · - ·                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------|-----|------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function<br>Name | I/O | After Reset<br>Release | Alternate Function                                  | Function                                                                                                                                                                                                                                                                                                                                                  |  |

| P00              |     | Input port             | TI00/TBCLK0/(TAO)/(INTP8)                           | Port 0. 7-bit I/O port. Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P01, P03 and P04 can be set to TTL input buffer. Output of P00 and P02 to P04 can be set to N-ch open-drain output (EVDD tolerance). P02, P03 and P04 can be set to analog input. |  |

| P01              |     |                        | TO00/TBCLK1/TAIO/(INTP10)                           |                                                                                                                                                                                                                                                                                                                                                           |  |

| P02              | I/O | Analog<br>function     | ANI11/SDO10/TXD1/VCIN10/CTxD0                       |                                                                                                                                                                                                                                                                                                                                                           |  |

| P03              |     |                        | ANI10/SDI10/RXD1/SDA10/VCIN11/CRxD0                 |                                                                                                                                                                                                                                                                                                                                                           |  |

| P04              |     |                        | ANI13/SCLK10/SCL10                                  |                                                                                                                                                                                                                                                                                                                                                           |  |

| P05              |     | Input port             | (INTP10)                                            |                                                                                                                                                                                                                                                                                                                                                           |  |

| P06              |     |                        | (INTP11)/(TAIO)                                     |                                                                                                                                                                                                                                                                                                                                                           |  |

| P10              |     | Analog function        | SCLK11/SCL11/TMIOB1/ANI9                            |                                                                                                                                                                                                                                                                                                                                                           |  |

| P11              |     |                        | (RxD0)/SDI11/SDA11/TMIOD1/(TMIOA1)/ANI8             |                                                                                                                                                                                                                                                                                                                                                           |  |

| P12              |     | Input port             | (TxD0)/SDO11/TMIOA1/(TMIOB0)/(INTP5)                | Port 1.                                                                                                                                                                                                                                                                                                                                                   |  |

| P13              | I/O |                        | TXD2/SDO20/TMIOC1/(TMIOD1)/IrTxd                    | 8-bit I/O port. Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be specified by a software setting at input port. Input of P10 and P14 to P17 can be set to TTL input buffer.                                                                                                                                        |  |

| P14              |     |                        | RXD2/SDI20/SDA20/TMIOB0/(TMIOC1)/(SCL A0)/IrRxd     |                                                                                                                                                                                                                                                                                                                                                           |  |

| P15              |     |                        | SCLK20/SCL20/TMIOD0/ (SDAA0)                        |                                                                                                                                                                                                                                                                                                                                                           |  |

| P16              |     |                        | TI01/TO01/INTP5/TMIOC0/(SDI00)/ (RXD0)<br>/(TMIOA1) | Output of P10, P11, P13 to P15, and P17 can be set to N-ch open-drain output (EVDD tolerance). P10 to P11 can be set to analog input.                                                                                                                                                                                                                     |  |

| P17              |     |                        | TI02/TO02/TMIOA0/TMCLK0/(SDO00)<br>/(TXD0)/(TMIOD0) |                                                                                                                                                                                                                                                                                                                                                           |  |

| P20              |     |                        | ANIO/AVREFP/VCIN12/(INTP11)                         |                                                                                                                                                                                                                                                                                                                                                           |  |

| P21              |     |                        | ANI1/AVREFM/VCIN13                                  |                                                                                                                                                                                                                                                                                                                                                           |  |

| P22              |     | Analog<br>function     | ANI2/ANO0/PGA0IN/VCIN0                              | Port 2.<br>8-bit I/O port.                                                                                                                                                                                                                                                                                                                                |  |

| P23              | 1/0 |                        | ANI3/ANO1/PGA0GND                                   |                                                                                                                                                                                                                                                                                                                                                           |  |

| P24              | I/O |                        | ANI4/PGA1IN                                         | Input/output can be specified in 1-bit units.                                                                                                                                                                                                                                                                                                             |  |

| P25              |     |                        | ANI5/PGA1GND                                        | Can be set to analog input.                                                                                                                                                                                                                                                                                                                               |  |

| P26              |     |                        | ANI6                                                |                                                                                                                                                                                                                                                                                                                                                           |  |

| P27              |     |                        | ANI7                                                |                                                                                                                                                                                                                                                                                                                                                           |  |

| P30              |     |                        | INTP3/RTC1HZ/SCLK00/SCL00/TAO                       | Port 3.<br>2-bit I/O port.                                                                                                                                                                                                                                                                                                                                |  |

|                  |     |                        | /(TMIOB1)                                           | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specified                                                                                                                                                                                                                                                        |  |

| P31              | I/O | Input port             | TI03/TO03/INTP4/(CLKBUZ0)/(TAIO)                    | by a software setting at input port. Input of P30 can be set to TTL input buffer. Output of P30 can be set to N-ch open-drain output (EVDD tolerance).                                                                                                                                                                                                    |  |

|                  |     |                        | /VCOUT1                                             |                                                                                                                                                                                                                                                                                                                                                           |  |

(2/2)

|                  |            |                     |                                    | (2/2)                                                                                                                                                                                                                                       |  |

|------------------|------------|---------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Function<br>Name | I/O        | After Reset Release | Alternate Function                 | Function                                                                                                                                                                                                                                    |  |

| P40              |            |                     | SWDIO                              | Port 4.                                                                                                                                                                                                                                     |  |

| P41              |            |                     | (TAIO)                             | 4-bit I/O port. Input/output can be specified. Use of an on-chip pull-up resistor can be                                                                                                                                                    |  |

| P42              | I/O        | Input port          | (INTP8)                            |                                                                                                                                                                                                                                             |  |

| P43              |            |                     | (INTP9)                            | specified by a software setting at input port.                                                                                                                                                                                              |  |

|                  |            |                     | INTP1/SDI00/RXD0/SDA00/TBIO0/(TAO) | 00/TBIO0/(TAO)                                                                                                                                                                                                                              |  |

| P50              |            | Input port          | /(TMIOC1)/(CRxD0)                  | Port 5. 6-bit I/O port.                                                                                                                                                                                                                     |  |

|                  |            |                     | INTP2/SDO00/TXD0/TBIO1/(TMIOD1)/(C | Input/output can be specified in 1-bit units.  Use of an on-chip pull-up resistor can be specified  by a software setting at input port.                                                                                                    |  |

| P51              | I/O        |                     | TxD0)                              |                                                                                                                                                                                                                                             |  |

| P52              | 1/0        |                     | (INTP1)                            |                                                                                                                                                                                                                                             |  |

| P53              |            |                     | (INTP2)                            | Input of P50 and P55 can be set to TTL input buffer.                                                                                                                                                                                        |  |

| P54              |            |                     | (INTP3)                            | Output of P50, P51, and P55 can be set to N-ch open-drain output (EVDD tolerance).                                                                                                                                                          |  |

| P55              |            |                     | (INTP4)/(CLKBUZ1)/(SCLK00)         |                                                                                                                                                                                                                                             |  |

| P60              |            |                     | SCLA0                              | Port 6.                                                                                                                                                                                                                                     |  |

| P61              |            |                     | SDAA0                              | 4-bit I/O port. Input/output can be specified in 1-bit units. Output of P60 and P63 is N-ch open-drain output (6 V tolerance).                                                                                                              |  |

| P62              | I/O        | Input port          | SS00                               |                                                                                                                                                                                                                                             |  |

| P63              |            |                     | _                                  |                                                                                                                                                                                                                                             |  |

| P70              |            | ) Input port        | KR0/SCLK21/SCL21/(VCOUT1)          |                                                                                                                                                                                                                                             |  |

| P71              |            |                     | KR1/SDI21/SDA21/(VCOUT0)           | B-4.7                                                                                                                                                                                                                                       |  |

| P72              |            |                     | KR2/SDO21                          | Port 7. 8-bit I/O port. Input/output can be specified in 1-bit units. Use of an on-chip pull-up resistor can be specified by a software setting at input port. Output of P71 and P74 can be set to N-ch open-drain output (EVDD tolerance). |  |

| P73              |            |                     | KR3/SDO01                          |                                                                                                                                                                                                                                             |  |